さて、Vivadoも入れ準備ができたので、まずは公式のTutorialに沿って試してみます。

Getting Started with Vivado [Reference.Digilentinc]

この公式のTutorialで使っているVivadoは2016.2というかなり古いバージョンなので今回私が使っている2019.1とはGUIがまるっきり違ってますのでお気を付けください。

このTutorialはVivadoでLチカ回路を作る!ってよくあるタイプのチュートリアルです。

ZynqのFPGA部分(PL)で作成するということでしょう。

ちなみにZynqってのはCortexメインのPS(ProcessingSystem)領域と、FPGAのPL(ProgrammableLogic)領域に分かれており、それぞれPS/PLというようです。

VivadoというツールはHW部の生成に使いますからFPGA部(PL領域)ということになりますね。

このPSだPLだってのがSoCなFPGAを使ってきたことのない私には初見になります。

プロジェクトの設定

Vivadoを起動します。

Create Project から Next と進みプロジェクト名を入力します。

locationは各自に合わせて適当に。Project名はTutorialに合わせて blinky にしました。

そしてNext

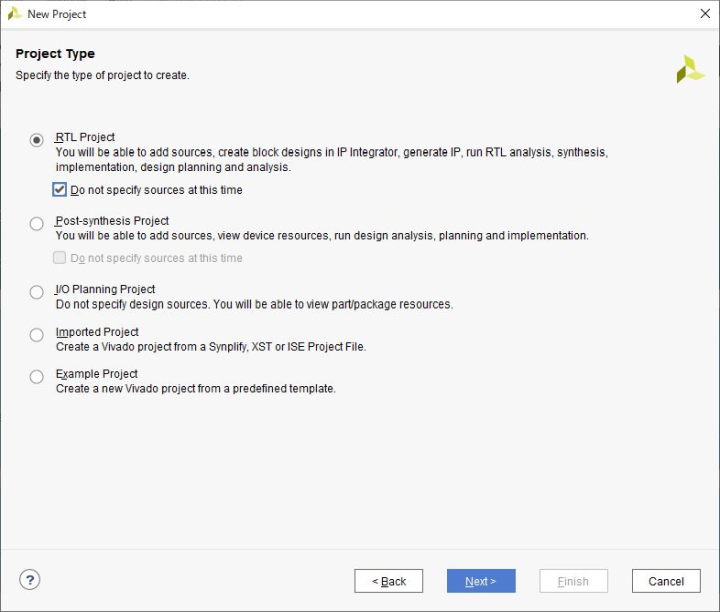

ProjectTypeはRTL Projectで、ソースファイルは指定しないのでチェック入れてからNext。

Default PartではZYBOのボードを指定します。市販ボードを使う場合ここが楽でいいですよね。

Z7-10を指定しますが、TutorialではZyboと古いボードでの設定になっているようですので注意が必要です。

ただ、最初はZYBOが出てこなかったので、右上にある Update Board Repositories をクリックして、10分くらい待つとZYBOが出てきました。この時間でボード情報をダウンロードしてきたようです。長すぎてハングしたのかと思ってKillするところでしたよ。

で、出てきたZyboのZ7-10を選択してからNext。

設定は終わりです。Finish。

合成してみる

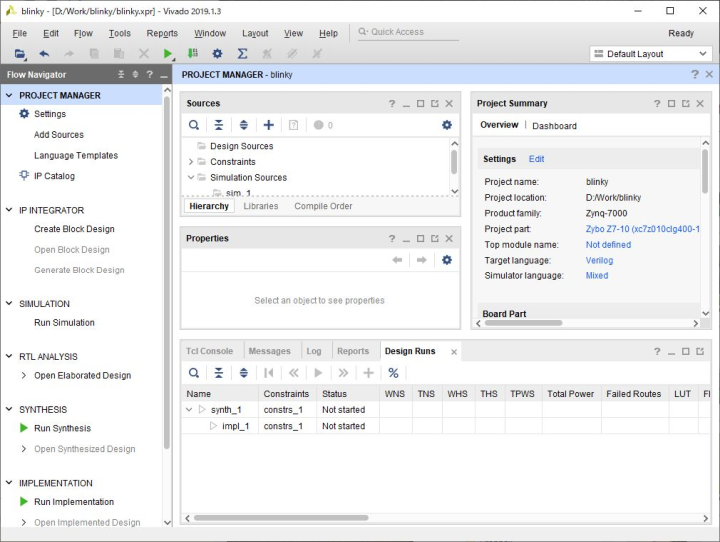

Vivadoが立ち上がったかと思います。

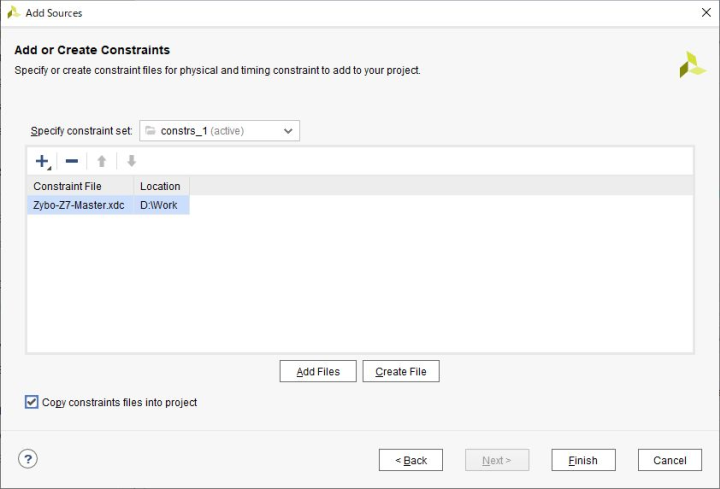

まずは色々な制約を指定する ConstraintFile を追加します。

左メニューのAdd Sourcesをクリックします。

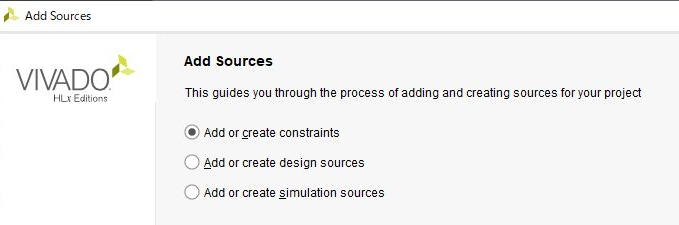

Add or create constraints を選択してNext。

ここで、TutorialのページにあるZIP Archiveをダウンロードして展開しておきます。

zipはここらへんにありますよ。

Add Files(若しくは+アイコン→Add Files)をクリックして制約ファイルを指定します。

Tutorialでは Zybo-Master.xdc を指定していますが、Z7-10の場合は Zybo-Z7-Master.xdc ですね。間違わないように。

どれが正しいのか?ってのは、ファイルの中を見てたとえばクロックピンの指定を見ればわかるかと思います。

そして、 Copy constraints files into project にチェックを入れてFinish。

Copyのチェックを入れたので自分の指定したディレクトリ内にコピーされているはずです。

Project ManagerのSourcesペインの中のConstraints(1)の左の>をクリックして展開し、

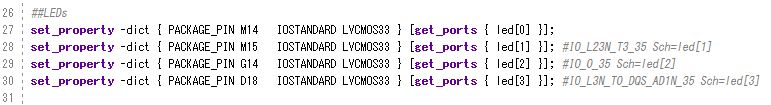

今読み込ませた Zyno-Z7-Master.xdc をダブルクリックしてファイルの中を見てみます。

制約が色々と書いてありますが、すべて#でコメントアウトされていますのでこのままでは何の意味もありません。

なので、この中から必要な部分だけコメントを外します。

8、9行目のクロック

#set_property -dict { PACKAGE_PIN K17 IOSTANDARD LVCMOS33 } [get_ports { sysclk }]; #IO_L12P_T1_MRCC_35 Sch=sysclk

#create_clock -add -name sys_clk_pin -period 8.00 -waveform {0 4} [get_ports { sysclk }];LED[0]の27行目

#set_property -dict { PACKAGE_PIN M14 IOSTANDARD LVCMOS33 } [get_ports { led[0] }]; #IO_L23P_T3_35 Sch=led[0]この行頭の#を外します。

意味としては、クロックの方はsysclkっていうピンのパッケージの位置とIO規格の指定。加えてクロックの属性(周期8ns(デューティ50%)=125MHz)の指定。

LEDの方はパッケージの位置とIO規格の指定です。

コメント外したらセーブします(フロッピーアイコンをクリック)。

次はRTL(Verilog)を書いていきます。

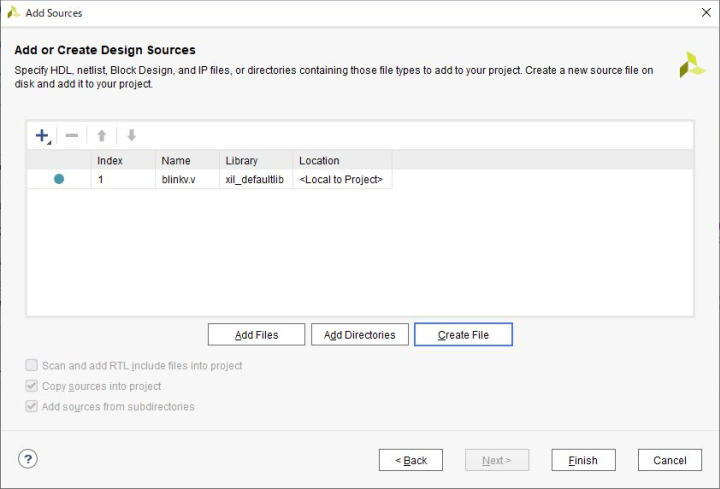

PROJECT MANAGERから Add Sourcesをクリック。

Add create design sources を選択してNext。

新規に作るのでCreate File で ファイル名は blinkv.v といれてOK。

これでFinish。

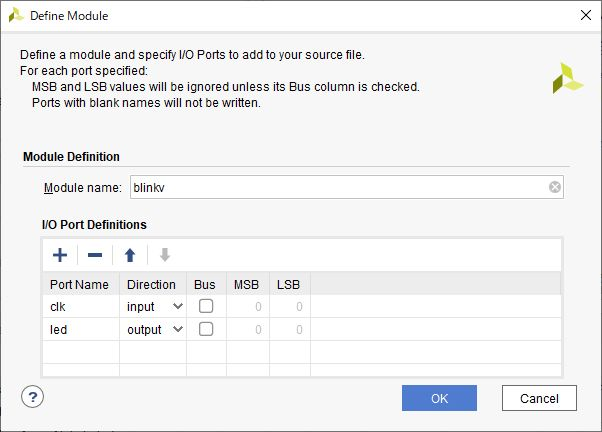

すると、新規ファイルだからかモジュールの定義を聞いてきますので、以下のように入力してOK。

ここで間違いに気づいた方は訂正してお進みください。今回はエラーの確認もあるので間違ったまま進めます。

すると、今作成したblinkv.vがSourcesペインに現れたのでそれをダブルクリックして開きます。

拡大してみます。

先ほど指定した入出力しか定義されていません。

これでは何も動きませんので、論理を実装してみます。

やることはLEDチカチカなので、まず必要なのはカウンターですね。

クロックとリセットがあればできますが、リセットってPSのリセットしか回路にはないようです。なので無視しちゃいましょう。

クロックはPSとPL両方にあるようですからPLの方を使用します。

ちなみにPLにクロックがない場合は。PSの方から与えてやる必要があるようで、Zynqの方の設定がいるようです。

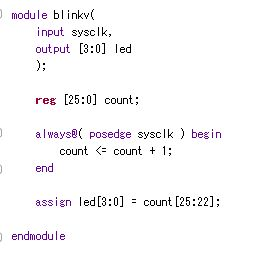

超簡単なLEDチカチカはこんな感じでしょうか。セーブを忘れずに

内容は言うまでもないでしょうが、24ビットカウンタを作って一番上のビットをledに直結です。

さて、合成していましょう。

いきなりGenerate Bitstreamでもいいんでしょうが、ここは順番に行ってみます。

Run Synthesis

動いているかどうかわかりにくいんですが、右上を見ればわかります。

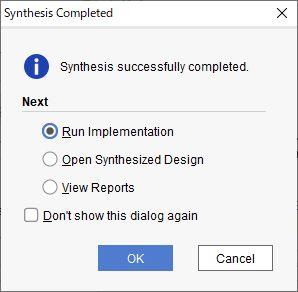

無事終われば次はRun Implementation。

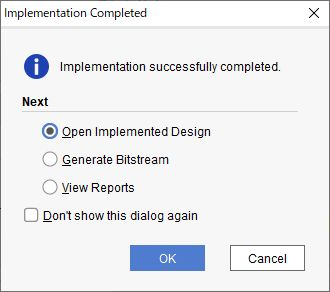

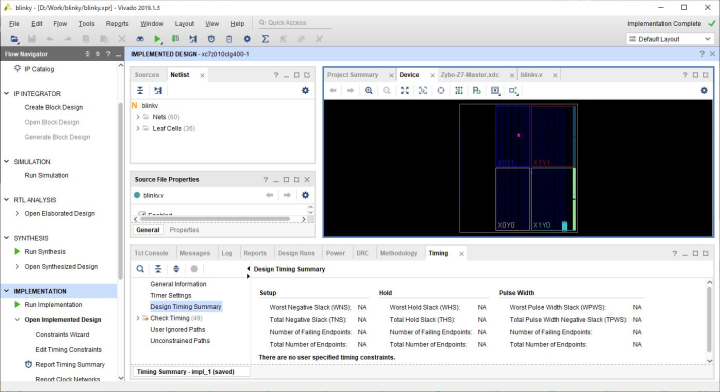

無事終われば次はOpen Implementerd Designを選んでみましょう。

ちょこっとだけ使ってますよーって感じで出てきました。

ちなみにSYNTHESISの中のSchematicをクリックすれば回路図も見れます。

あまり見やすい回路図ではないですけどね。

で、最後に

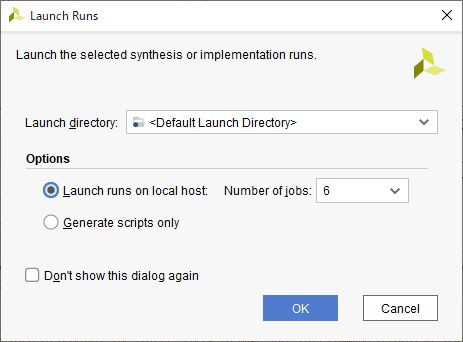

Generate Bitstream → OK

ジョブ数ってのはPCの使用するコア数ってことなんですかね。まぁ適当に。

で、先に書いたようにソースに間違いがあるのでエラーが出ます。

っていうかここまで来ないとエラーが出ないんですね。ちゃんとメッセージ見てればWarningとか出てたのかもしれません。

[DRC NSTD-1] Unspecified I/O Standard: 2 out of 2 logical ports use I/O standard (IOSTANDARD) value ‘DEFAULT’, instead of a user assigned specific value. This may cause I/O contention or incompatibility with the board power or connectivity affecting performance, signal integrity or in extreme cases cause damage to the device or the components to which it is connected. To correct this violation, specify all I/O standards. This design will fail to generate a bitstream unless all logical ports have a user specified I/O standard value defined. To allow bitstream creation with unspecified I/O standard values (not recommended), use this command: set_property SEVERITY {Warning} [get_drc_checks NSTD-1]. NOTE: When using the Vivado Runs infrastructure (e.g. launch_runs Tcl command), add this command to a .tcl file and add that file as a pre-hook for write_bitstream step for the implementation run. Problem ports: clk, and led.

xdcで指定しているポート名とVerilogソースの中で指定しているポート名が違ってますので、xdc指定が反映されていなかったってことになりますね。

clkはsysclkでわかるけど、ledもダメなのか。xdcでled[0]としてたからか。

なので、xdcの方は変えずにVerilogの方を以下の様に変更して、再度 Generate Bitstream。

これで無事OKとなりました。

実機確認

さて、実際に動かしてみます。

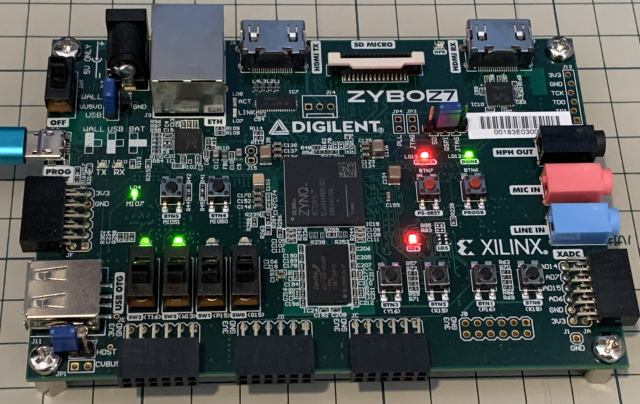

Z7-10ボードのJ12 PROG UARTと書いてあるUSB端子とパソコンを通信のできるUSBケーブルで接続します。

JP6(電源選択)はUSB側に、JP5(Config選択)はJTAGにしておきます。

それでスライドスイッチをON

パソコンで認識がされたかと思います。私の環境ではCOM4が増えました。

また、電源を入れたら勝手に動き始めました。デフォルトでプログラムされているんですね。

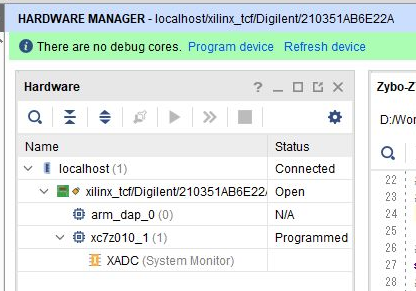

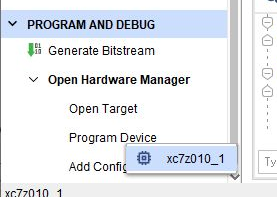

次にFlowNavigatorの一番下。Open Hardware Managerの下の

Open Target → AutoConnect をクリックします。

Hardwareペインにデバイスが現れました。

書き込みます。

Program Device → xc7z010_1

ここで、ビットストリームファイルに先ほどできたbitファイルを指定します。

bitファイルはどこにあるの???で探したら .\blinky.runs\impl_1 の下にできてました。

でProgramをクリック。

Programが終わると自動で起動します。

LED0が速いペースで点滅しているかと思います。ちょっと速すぎましたね。

よくクロックみたら125MHzなんですよね。いやぁ普通の基板でシングルエンドのクロックで125MHzなんていれてるんですね。ちょっとびっくりです。

もう2ビットくらいカウンター増やしたほうがいいかと思います。

おまけ

まぁこれで終わるのも寂しいので、ちょっと拡張してみましょう。

まず、LEDを4bit使いましょう。せっかく4個並んでいるんですからね。

そして、4bitの光らせ方を変えてみましょう。

Verilogソースとxdcを以下のように書き換えます。

合成、ビットストリーム作成、Programの流れは今までと同じです。

2ビット増やしたカウンターの上位4ビットをそのまま点滅に使ってます。2bit増やして一番上位の25ビット目がちょうどいい感じになりました。

さらにここからさらにひとひねりしてみましょう。

おっさんなら知っているナイトライダーをするってのもありですね。えぇ昔は良くやってました。

今回は一番手っ取り早くLホワをしてみます。

LEDがチカチカ点滅するのがLチカ。

LEDがホワーっと点滅するのがLホワ。

そのLホワです。

LEDは一般的にはPWM制御で明るさを制御します。パルスの幅で制御するわけですが、それを手っ取り早く実現してみます。

カウンターまでは一緒。LEDへのアサインを変えるだけです。

これ、どういう動きをするの?って結構面倒ですが、考えてみるのも楽しいですよ。

4つのLEDにちょっとづつ違うようにアサインしてみましたが、基本は1行で実現できます。

まぁこれは一方向だけのホワなので厳密なLホワじゃないでしょうけど、1行でできるので簡易テストにはちょうどいいです。

そこをちゃんとするのは考えてみてください。数行増えるだけでいけますね。

まぁこれもVerilogだから簡単なのであって、スケマティックで書くとなると面倒にはなりますけどね。

というわけで、PL領域で遊んでみました。

ここまではPS領域にあるCortexはまったく動いていない状態です。たんなるFPGAですね。

次はPS領域を動かしてみたいと思います。

コメント

はじめまして。

記事読まさせていただきました。

お忙しいところ恐縮ですが、ご質問なのですが、

一方向だけのホワではなくなく厳密な両側Lホワのverilog記述を

教えては頂けませんでしょうか?

コメントありがとうございます。

まず最初にLホワの回答は一つではありません。

LホワっていうのはLED自体の制御はLチカと同じく1-0の制御ではありますが、その1-0の時間を常に変更していくことで実現しています(PWM制御)。

どのように光らせたいのか?によって1-0の時間配分を変えていく回路を考えないといけません。

例として挙げたカウンタの上位と下位との単純比較を用いてますので1-0比率がリニアに変わっていきます。

LED自体の光り方の特性もあるのでリニアな感じには見えないかと思いますし、この回路の場合消灯がほぼ見えない感じになっているかと思います。

もっと明るい時間を増やしたいとか、もっと暗い時間を増やしたい。もっと余韻を引くようにしたい等々どう光らせたいかによって制御が変わってきますし、より複雑になるでしょう。

ただ単純に、私の例の光り方で両方向を作りたいのであれば、

led[3]とled[2]の光り方を繰り返せばいいので、例えばもう1ビット増やしてそれをフラグとして

count[26] ? count[25:22] > count[7:4] : count[25:22] < count[7:4]; とすれば両方向にはなります。これも1行で実現出来ますね。 これとは違ったホワ具合にしたい等々考えるのも楽しいので是非実現方法を考えてみてください。 色々な方法があるかと思います。

ご回答頂き有難うございした。

ご連絡頂いたコードにて両側の”Lホワ”が実現出来ました。

出来たのですが、そのコードの詳細説明を求められており、

自分はverilogに疎く説明するのに困っております。

そこで再度ご質問させてください。

①なぜcount[26]をセレクタのセレクト信号になさっているのでしょうか?

②count[25:22] > count[7:4]この比較の意味はどういう意味でしょうか?

count[25:22] > count[3:0]でも問題ないのでしょうか?

③count[25:22] count[3:0]でも問題ないのでしょうか?

お忙しいところ恐縮ですがご教授のほどよろしくお願い申し上げます。

ご回答頂き有難うございした。

ご連絡頂いたコードにて両側の”Lホワ”が実現出来ました。

出来たのですが、そのコードの詳細説明を求められており、

自分はverilogに疎く説明するのに困っております。

そこで再度ご質問させてください。

①なぜcount[26]をセレクタのセレクト信号になさっているのでしょうか?

②count[25:22] > count[7:4]この比較の意味はどういう意味でしょうか?

count[25:22] > count[3:0]でも問題ないのでしょうか?

③count[25:22] count[3:0]でも問題ないのでしょうか?

お忙しいところ恐縮ですがご教授のほどよろしくお願い申し上げます。

③count[25:22] count[3:0]でも問題ないのでしょうか?

お忙しいところ恐縮ですがご教授のほどよろしくお願い申し上げます。

伊右衛門さん コメントありがとうございます。

Verilogのコードの説明をどなたかにしないといけないということは

何らかの課題なり宿題ってことでしょうか?

それをまるごと私が教えるのは伊右衛門様のためにもならないでしょう。

動作自体は非常にシンプルなものです。

基本はカウントアップしていくカウンタの一部を使って比較しているだけですから、

なぜこうなるのか?はよく考えないとわからないかもしれませんが、

シミュレーションするなり机上で考えるなりすればわかってくるかと思います。

たとえば

count[25:22] > count[3:0]でも問題ないのか?

という点においては実際に試してみれば挙動がどう変わるかわかるかと思います。

そういったことをされて、それでもわからない場合は、

自分なりにどう解釈してどう理解しようとしてどうわからなかったのか

を記載していただき再度コメントいただければと思います。

そこまでしたくないってことであれば他を当たっていただければと思います。

お忙しいところご返信頂き有難うございました。

おっしゃる通りでした。

シミュレーションや実機で試して

まずは自分で考えてみます。

それで考えがまとまったら再度

コメントさせて下さい。

有難うございました。

伊右衛門様

ご理解いただきありがとうございます。

こういったものの理解は机上の理解も大事ですが、まず試してみるってのも大事ですので、色々と気になったことは実際に試してみて理解を深めていかれてはと思います。

助言やアドバイス程度であればいくらでも行いますので、その際はコメントください