ZYBOさんですが、一通り動作できたので、次は公式にあった下記のHDMI Demoってのを試してみます。

Zybo Z7 HDMI Demo [Reference.Digilentinc]

GitHubにあるので、そこからダウンロード

GitHub – Digilent/Zybo-Z7-10-HDMI

かと思ったら違うようで、ここから最新のZIPファイルを落としてねってこと見たいです。

Releases · Digilent/Zybo-Z7-10-HDMI · GitHub

最新っていってもVivado2018.2が最新のようですね。

ZIPを適当なフォルダに展開します

このvivado_projの下に zybo-z7-10-hdmi.xpr があるので、これをVivadoから開いています。

ここは最新のVivado2019.2.1でやってみましょう。

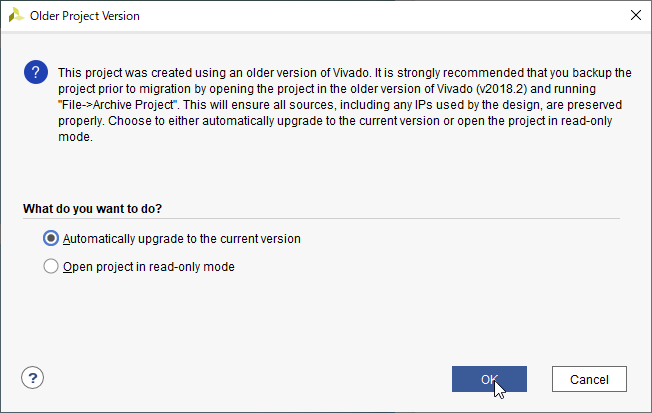

Open Projectで先のファイルを指定すると古いバージョンで作られたんやから自動でアップデートしまひょか?って聞かれるのでお任せしてみます。

IPのアップデートとかあるんで、素直に動くのかどうか。。。

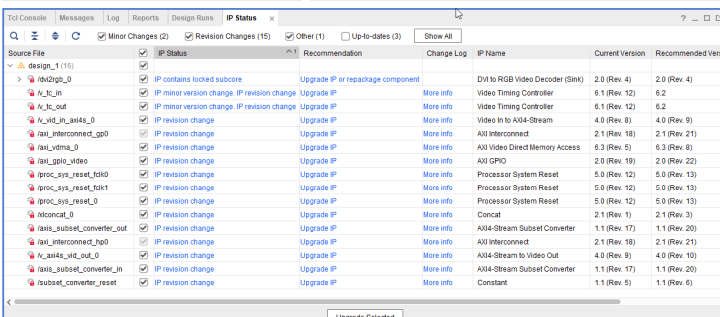

Report IP Statusをクリックするとこんなにありまっせ!アップグレードお勧めしまっせって出てきました。

全てIPが選択されているので、Upgrade Selected (上の画面の下に半分見切れているボタン)をクリックしてみます。 その後出てくるウィンドウでOKをクリック。

一応終わりました。

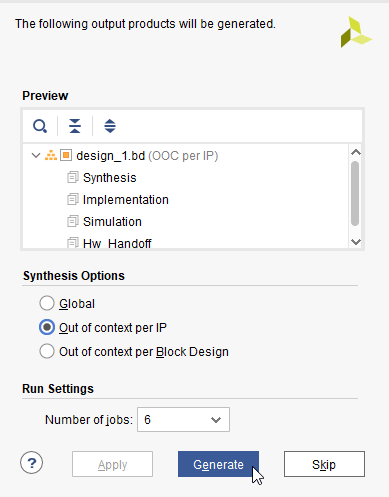

その後出てくるウィンドウでGenerate

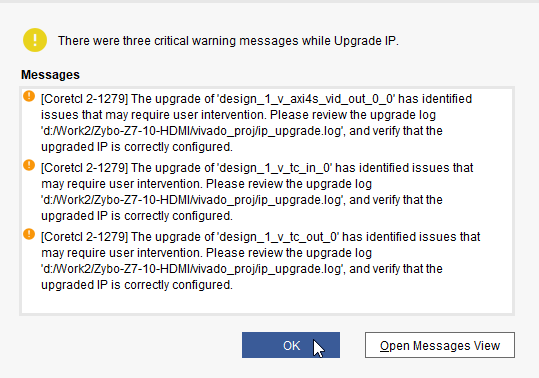

2個のクリティカルワーニングが出てきました。

ila_refclkとila_pixclkについてなんか怒られてます。

OK押すとまた別のエラーが出ました。

Messageウィンドウに出てきた ip_update.log をクリックすると中身が見れました。

中を見ていくと Upgradeの SUCCESS とそうでないものがわかります。

design_1_v_tc_out_0

IPのパラメータが違う?

An attempt to modify the value of disabled parameter ‘GEN_F0_VSYNC_HSTART’ from ‘640’ to ‘1280’ has been ignored for IP ‘design_1_v_tc_out_0’

An attempt to modify the value of disabled parameter ‘GEN_F0_VSYNC_HEND’ from ‘695’ to ‘1280’ has been ignored for IP ‘design_1_v_tc_out_0’

An attempt to modify the value of disabled parameter ‘GEN_F0_VBLANK_HSTART’ from ‘640’ to ‘1280’ has been ignored for IP ‘design_1_v_tc_out_0’

An attempt to modify the value of disabled parameter ‘GEN_F0_VBLANK_HEND’ from ‘640’ to ‘1280’ has been ignored for IP ‘design_1_v_tc_out_0’

An attempt to modify the value of disabled parameter ‘GEN_F1_VSYNC_HSTART’ from ‘695’ to ‘1280’ has been ignored for IP ‘design_1_v_tc_out_0’

An attempt to modify the value of disabled parameter ‘GEN_F1_VSYNC_HEND’ from ‘695’ to ‘1280’ has been ignored for IP ‘design_1_v_tc_out_0’

An attempt to modify the value of disabled parameter ‘GEN_F1_VBLANK_HSTART’ from ‘640’ to ‘1280’ has been ignored for IP ‘design_1_v_tc_out_0’

An attempt to modify the value of disabled parameter ‘GEN_F1_VBLANK_HEND’ from ‘640’ to ‘1280’ has been ignored for IP ‘design_1_v_tc_out_0’

上記のパラメータの変更がダメだって???

同様に design_1_v_tc_in_0 も

An attempt to modify the value of disabled parameter ‘GEN_F0_VSYNC_HSTART’ from ‘640’ to ‘1280’ has been ignored for IP ‘design_1_v_tc_in_0’

An attempt to modify the value of disabled parameter ‘GEN_F0_VSYNC_HEND’ from ‘695’ to ‘1280’ has been ignored for IP ‘design_1_v_tc_in_0’

An attempt to modify the value of disabled parameter ‘GEN_F0_VBLANK_HSTART’ from ‘640’ to ‘1280’ has been ignored for IP ‘design_1_v_tc_in_0’

An attempt to modify the value of disabled parameter ‘GEN_F0_VBLANK_HEND’ from ‘640’ to ‘1280’ has been ignored for IP ‘design_1_v_tc_in_0’

An attempt to modify the value of disabled parameter ‘GEN_F1_VSYNC_HSTART’ from ‘695’ to ‘1280’ has been ignored for IP ‘design_1_v_tc_in_0’

An attempt to modify the value of disabled parameter ‘GEN_F1_VSYNC_HEND’ from ‘695’ to ‘1280’ has been ignored for IP ‘design_1_v_tc_in_0’

An attempt to modify the value of disabled parameter ‘GEN_F1_VBLANK_HSTART’ from ‘640’ to ‘1280’ has been ignored for IP ‘design_1_v_tc_in_0’

An attempt to modify the value of disabled parameter ‘GEN_F1_VBLANK_HEND’ from ‘640’ to ‘1280’ has been ignored for IP ‘design_1_v_tc_in_0’

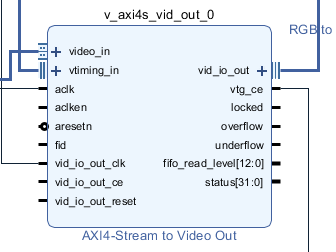

design_1_v_axi4s_vid_out_0_0

こちらはポートが違う

fifo_read_level っていうポートが追加されている?

でした。

うーん。バージョンが違うってやっかいですね。

ブロック図を見てみます。

まずは右下にあるv_axi4s_vid_out_0

fifo_read_level[12:0] っていうポートがあります。これが増えてるってことなんでしょう。

ドキュメント見てもよくわからんですね。無視してよさそうです。

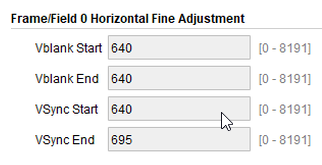

次にdesign_1_v_tc_out_0 です。

パラメータの設定に問題があるようです。

IPをダブルクリックして Default/Constantのタブを見てみます。

例えばこのエラー

An attempt to modify the value of disabled parameter ‘GEN_F0_VSYNC_HSTART’ from ‘640’ to ‘1280’ has been ignored for IP ‘design_1_v_tc_out_0’

このVSync Start かと思われます。ここを1280にできませんってことなんでしょうか。

元々のIPの設定はどこにあるのか?と探してみたら

vivado_proj\zybo-z7-10-hdmi.srcs\sources_1\bd\design_1\ip\design_1_v_tc_in_0\design_1_v_tc_in_0.xci

にありました。

この中を見ると、該当する箇所が見つかります。

たとえば、先のGEN_F0_VSYNC_HSTART もともとは1280に設定しようとしています。

ただ、元のファイルも720Pとしての設定のようです。

<spirit:configurableElementValue spirit:referenceId=”PARAM_VALUE.VIDEO_MODE”>720p</spirit:configurableElementValue>

で、あればこちらも720Pの設定値のままでいいんじゃないの?ってことで、720Pのデフォルトのままにしておきます。

じゃぁ次はdesign_1_v_tc_in_0

先のoutもこのinも同じIPの様ですね。

inのこちらは検出のみ行っているようです。

自動検出なのでこちらにパラメータを設定するところはないはず。なのになぜ?

というわけで、これらの3つのIPのエラーはそのままにして進めてみます。

Generate Bitstream をクリック。

問題なく終わったので、

File → Export → Export Hardware

include bitstream にチェックを入れてOK

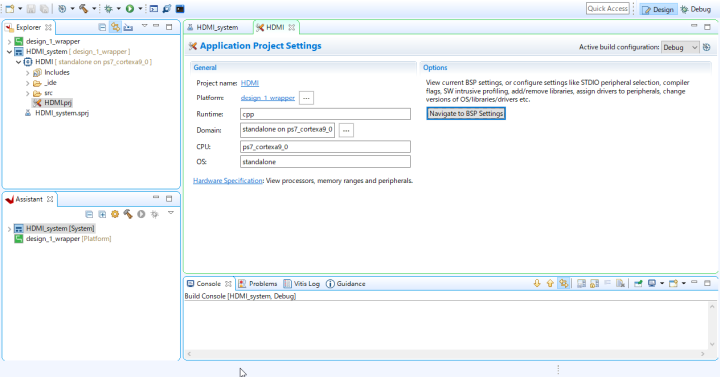

公式の方はSDKを起動してますが、2019.2なのでVitisを起動します。

Tools → Launch Vitis

新しいディレクトリを作って指定しておきました。

Vitisから File → New → Application Project

Project nameに HDMI と入力してNext

Platformのウィンドウになるので、Create a new platform from hardware (XSA) のタブを選び、+をクリックして先にVivadoで作成したできたdesign_1_wrapper.xsa を指定します。そしてNext

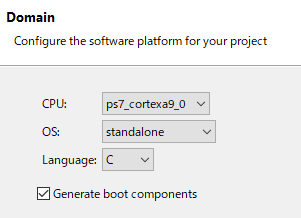

Domainはそのままで Next

TempalatesではEmpty Applicationを指定してFinish

Vitis IDEの画面が立ち上がりました。

プロジェクトを右クリックしてImport Sources

ディレクトリにZIPを展開してできたsdk_appsrcを指定します。

以下のチェックボックスのようにしてFinish

公式の方はここでHDMIケーブルつないでって言ってるけどBuildしなくていいのかな?

よくわかんないからBuildしておきましょう。

問題なくfinishしました

で、動かしてみます。

HDMI IN/OUTにケーブルをつなげろってありますが、今の我が家の環境ではINにつなげられるものが無いので、OUTだけをモニタに接続します。

そしてPROGUART端子にUSBケーブルをPCと接続しPCでTerminalを起動します。ボーレートは115200です。

Vitisの方から Xilinx → Program FPGA

出てきたウィンドウそのままでProgram

DONEの緑LEDが点きました。

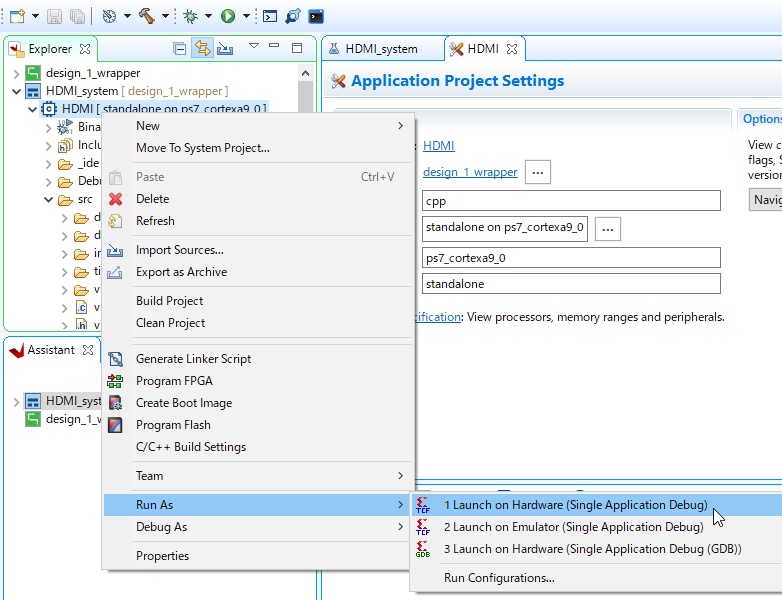

Projectを右クリックして Run As → Launch on Hardware (Single Application Debug)

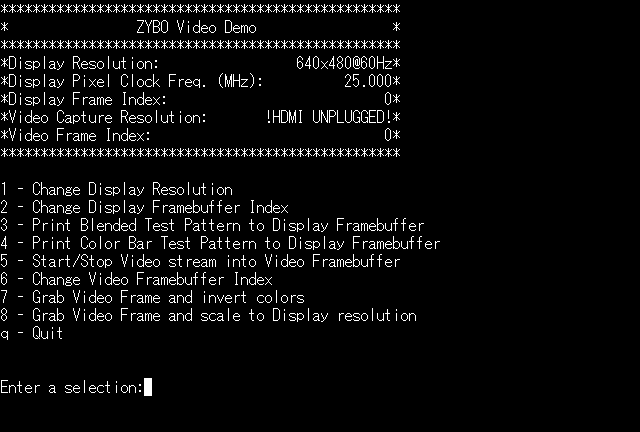

Terminalにこんなメッセージが出てきて、HDMIモニタにグラデーションのついたカラーバーが出てきました。

ちなみに解像度は、コンソールに出ているように640ⅹ480でした。

HDMIの入力を入れてたら、その解像度に合わせてくれるのかもしれません。

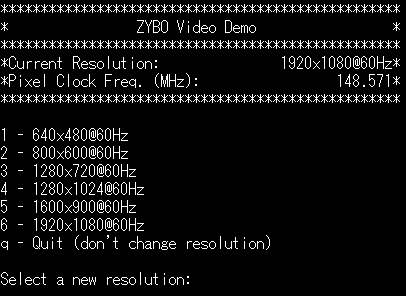

コンソールで先のメニューに対して1を入力すると解像度の選択が出てきます。

ここで6を指定すると1920ⅹ1080になりました。

ただ、カラーバーは640ⅹ480のままでしたけど。。。

違うメニューでちゃんと画面いっぱいにカラーバーがでるようにもなりましたし、違う画も出ました。

フレームバッファが3つあったり、HDMI Inからのキャプチャが出来たりするようです。

今の機材で、HDMI入力が試せなかったので、準備しておかないと。。

で、プロジェクトの中身を見てみると、何をHWでやって何をSWでやってってのがわかりますね。

SoCFPGAってのはこういう風に作っていくってことでしょうか?

テストパターンなんてソフトで書いてるんですね。フレームバッファに格納って意味なら一度だけ書けばいいので回路で実装よりはSWの方が合理的ですね。

ただ、ソースにある色々な関数やら定義が良くわからんです。

これもどっかのドキュメントに載ってるんですよね。探してみないとなぁ。

でも、ググったくらいじゃ見つからんのだけど。。。

コメント